When asked about memory barriers in an interview, you can answer systematically from three aspects: concept, classification, and core functions, and reflect your in-depth understanding by combining practical scenarios.

1. Brief Concept

A memory barrier (Memory Barrier / Memory Fence) is a hardware and software mechanism used to restrict the execution order of memory operations (loading/storing). It avoids logical errors in programs in multi-threaded or multi-processor environments caused by issues such as instruction reordering by processors or compilers and cache inconsistency.

2. Main Classifications

It can be divided into three categories according to the scope of action:

- Load Barrier: Ensures that all read operations before the barrier are completed before executing read operations after the barrier.

- Store Barrier: Guarantees that all write operations before the barrier are finished before executing write operations after the barrier.

- Full Barrier: Constrains both read and write operations at the same time, and all memory operations before and after the barrier are executed in strict order.

3. Core Functions (Illustrated with Scenarios)

- Prevent Instruction Reordering

Modern processors and compilers reorder instructions to optimize performance, but this may disrupt the logical order in multi-threaded situations. For example, after thread A updates a shared variable, it sets a “completion flag”. Without a store barrier, the flag may be set but the variable not updated, causing thread B to read incorrectly. A memory barrier can force the maintenance of the logical order of operations.

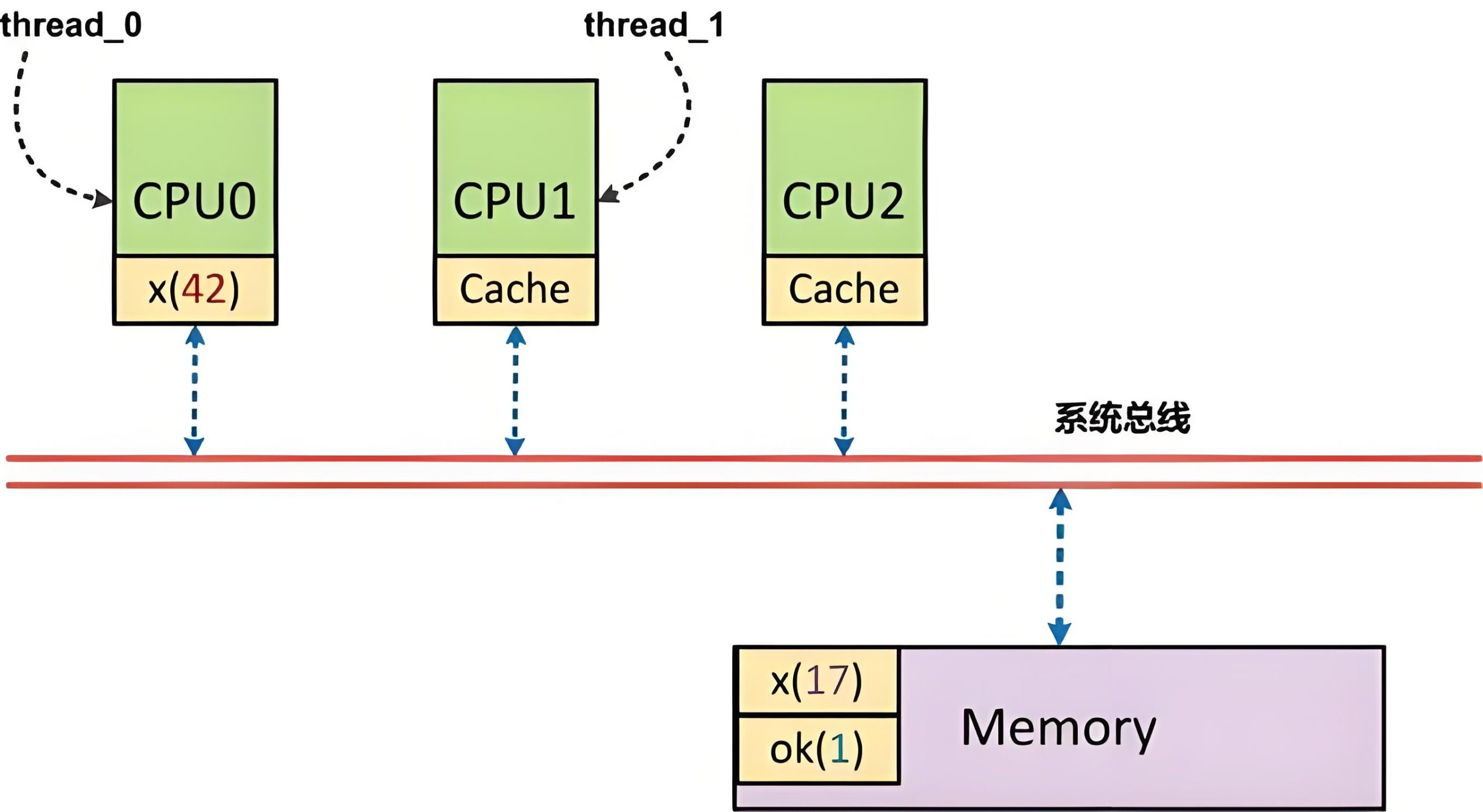

- Ensure Memory Visibility

In a multi-processor system, each core has an independent cache, and modified data may be temporarily stored in the cache without being synchronized to the main memory. A memory barrier triggers cache synchronization to ensure that writes from one processor can be seen by other processors in a timely manner. For instance, a store barrier flushes updates to a shared variable to the main memory, preventing other threads from reading old values.

- Support Concurrent and Low-Level Programming

In lock-free programming (such as lock-free queues), memory barriers coordinate the order of operations on shared data between threads to prevent race conditions. In operating system and driver development, they ensure the order of memory-mapped I/O operations (such as sending commands first and then reading hardware responses) to avoid the hardware receiving chaotic operation sequences.

Summary

In short, a memory barrier is an “order maintainer” in multi-threaded and multi-processor environments. It ensures the correctness of programs in concurrent scenarios by restricting the order of memory operations and synchronizing caches, and is a basic mechanism for low-level concurrent programming.